#### UNIT II ARM PROCESSOR AND PERIPHERALS

ARM Architecture Versions – ARM Architecture – Instruction Set – Stacks and Subroutines – Features of the LPC 214X Family – Peripherals – The Timer Unit – Pulse Width Modulation Unit – UART – Block Diagram of ARM9 and ARM Cortex M3 MCU.

#### <u>PART-A</u>

#### 1. Draw and compare von-Neumann and Harvard architecture.

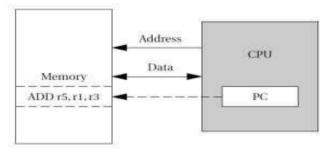

### Von Neumann Architecture

This kind of architecture consists of a single, shared memory for program and data. The computing system consist of a Central Processing Unit (CPU) and a memory. The CPU has several internal registers that store values used internally. One of these registers is the program counter (PC) which points to an instruction in memory. The memory holds data and instructions and can be read and written when given anaddress.

Fig. Von Neumann Architecture

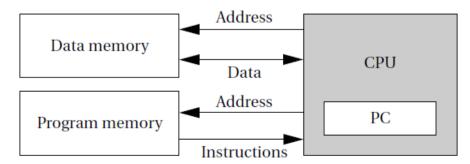

#### **Harvard Architecture**

This Kind of Architecture consist of separate memory for data and Program. The program counter points to program memory not data memory. Harvard Architecture are widely used today for separation of program and data memories provides higher performance for digital signal processing.

#### Fig. Harvard Architecture

## 2. In what ways CISC and RISC processors differ?

| CISC | the state of the second state of the second state              | RISC                                                              |

|------|----------------------------------------------------------------|-------------------------------------------------------------------|

| 1.   | It provides number of addressing modes                         | It provides very few number of addressing modes                   |

| 2.   | It has a micro programmed unit with a<br>control memory        | It has a hard wired unit without a control memory                 |

| 3.   | An easy compiler design                                        | Complex compiler design                                           |

| 4.   | Provides precise and intensive calculations slower than a RISC | Provides precise and intensive calculations faster<br>than a RISC |

## 3

## Define Load-Store Architecture in ARM Programming. (Nov/Dec-2013)

ARM is a load-store architecture-data operands must first be loaded into the CPU and then stored back to main memory to save the results.

## 4. List some of the features of ARM processor.

- ARM processors have a good speed of execution to power consumption ratio

- They have a wide range of clock frequency ranging from 1 MHz to few GHz

- ARM processors have built in hardware for debugging

- Supports enhanced instructions for DSP operations

## 5. Define memory width.

The memory width is the number of bits the memory returns on each access typically 8,16,32 or 64 bits.

The memory width has a direct effort on the overall performance and cost ratio.

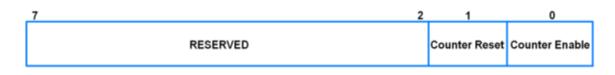

## 6. What is the use of Timer Control Register (TCR)?

- Timer Control Register is used to control the functions of timer/counter.It is used to enable/disable or reset the timer counter.Only the first two bits of the TCR must be used for these operations.

- > When the first bit is 1, the counters are enabled.

- When the second bit is 1, both the counters are reset on the next positive edge of the peripheral clock

## 7. Write down the steps required for PWM generation.

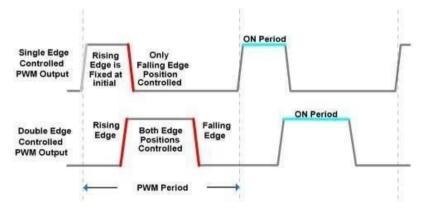

- Reset and disable PWM counter using PWM TCR

- Load prescale value according to need of application in the PWMPR

- > Load PWMMR0 with a value corresponding to the time period of your PWM wave

- > Load any one of the remaining six match registers with the ON duration of the PWM cycle.

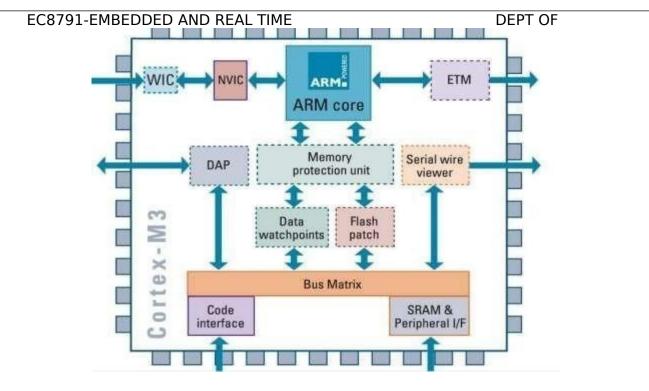

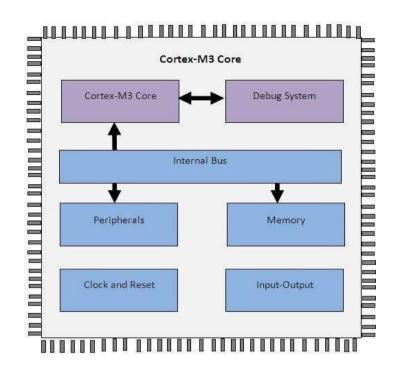

## 8. Why Cortex-M3 is needed in ARM processor?

- > Delivering higher performance and richer features

- Performance and energy efficiency

- ➤ Full featured

- $\triangleright$  Rich connectivity

9. Difference between timer and counter.

| Timer                                            | Counter                                        |

|--------------------------------------------------|------------------------------------------------|

| The register incremented for every machine       | The register is incremented considering 1 to 0 |

| cycle                                            | transition at its corresponding to an external |

|                                                  | input pin                                      |

| Maximum count rate is 1/12 of the oscillator     | Maximum count rate is 1/24 of the oscillator   |

| frequency                                        | frequency                                      |

| A timer uses the frequency of the internal clock | A counter uses an external signal to count     |

| and generates delay                              | pulses.                                        |

10. List the functions of ARM processor in supervisor mode.

The supervisor mode has privileges that user modes do not control of memory management unit is reserved for supervisor mode to avoid the obvious problems that could occur when program bugs cause inadvertent changes in the memory management registers.

## 11. Define Subroutine.

A subroutine is a block of code that performs a task based on some arguments and optionally returns a result. By convention we use registers R0 to R3 to pass arguments to subroutines and R0 to pass a result back to the callers. A subroutine that requires more than four inputs uses the stack for the additional inputs.

# 12. Define UART.

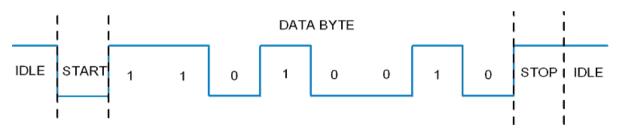

UART (Universal Asynchronous Reciever/Transmitter) is one of the earliest mode of communication applied to computer. The information is transmitted one binary bit at a time as such it is a serial communication method.

UART is asynchronous because it doesn't require a transmitter provided clock to synchronize the transmission and receipt of data.

13. List the functions of PWM.

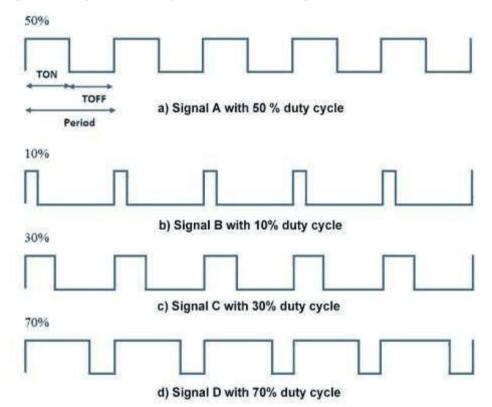

Pulse Width Modulation is a technique by which width of a pulse is varied while keeping the frequency constant. A period of a pulse consists of an ON cycle (HIGH) and an OFF cycle (LOW). The fraction for which the signal is ON over a period is known as duty cycle.

14.State any two data transfer and control flow instructions of ARM processor.Data transfer instructions used to transfer data between registers and memory.Memory to RegisterRegister to MemoryControl fow instructions are used to divert the flow of the program.Branch instructionCondition Codes

| E00701 |            |  |

|--------|------------|--|

|        | EMBENDED   |  |

|        | -EMIDEDDED |  |

|        |            |  |

Conditional branch

15.Suggest the rules which apply to ARM data processing instructions.

Data processing instructions can process one of their operands using the barrel shifter

Data processing instructions are processed within the Arithmetic Logic Unit (ALU)

ARM Processor is the ability to shift the 32 bit binary pattern in one of the source registers let or right by a specific number of positions before it enters the ALU.

16. What is meant by conditional execution?

Conditional execution is an event used to controls whether or not the core will execute an instruction. Most instructions have a condition attribute that determines if the core will execute it based on the setting of the condition flags.

- 17.List the registers associated with timers in LPC2148.

- Prescale register(PR)

- Prescale counter Register (PC)

- Timer control Register (TCR)

- Timer counter Register (TC)

- Count control Register (CTCR)

- Match control Register (MCR)

- Interrupt Register(IR)

18.State the function of co processor .

Co processor is a computer processor used to supplement the functions of the primary processor.Operations performed by the co processor may be floating point arithmetic, graphics, signal processing, string processing.

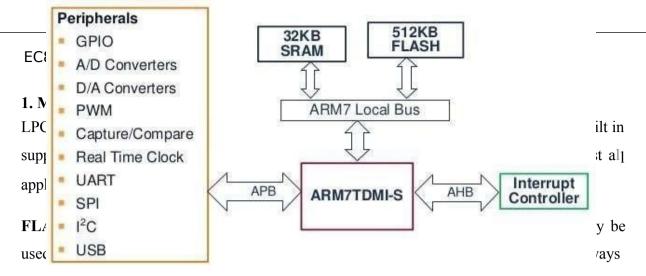

19.Mention the Key features of LPC2148X

- > 16 bit/32 bit ARM7TDMI-S microcontroller in a tiny LQFP64 package.

- 8KB to 40 KB of on-chip static RAM and 32 KB and 512 KB of on-chip flash memory.128-bit wide interface/accelerator enables high speed 60 MHZ operation.

- In system programming/In-Application programming (ISP-IAP) via on chip boot loader software.Single flash sector or full chip erase in 400 ms and programming of 256 B in 1 ms.

- Embedded ICE RT and Embedded Trace interfaces offer real time debugging with the on chip real monitor software and high speed tracing of instruction execution.

20.Difference between stack and stack pointer.

The difference between the stack and the stack pointer is that the stack is an area of memory, the stack pointer is the address of the last value pushed onto the stack.

21.Define peripheral devices.

Embedded systems that interact with the outside word means we need some form of peripheral

device. A peripheral device performs input and output functions for the chip by connecting to other devices or sensors that are off chip.

22.Mention the instruction set in ARM processor

- Data processing instructions

- Branch instrunctions

- Load store instructios

- Software interrupt instructios and

- Program status register instructions

#### PART-B

## 1. Draw the architecture of an ARM 9 processor and explain its functional units.

#### **ARM ARCHITECTURE**

- ARM was an acronym for Advanced RISC Machine. ARM is a family of computer processor designed by Advanced RISC Machine (ARM) Limited company.

- The architectural simplicity of ARM processors has traditionally led to very small implementations, which allow devices with very low power consumption. Implementation size, performance, and very low power consumption remain key attributes in the development of the ARM architecture.

- ARM Processor are used for low-power and low-cost applications like Mobile phones, Communication modems, Automotive engine management systems and Hand-held digital systems.

- ARM architecture has been developed since 1980s and most widely used 32-bit instruction set architecture.

#### RES OF ARM

- ARM Processors are based on reduced instruction set computing (RISC) architecture.

- □ 32-bit Architecture but also supports 16 bits or 8 bits data types

- $\Box$  32-bit processor register.

- □ 32-bit addresses.

- ARM Processors follow Load and Store type architecture where the data processing is performed only on the contents of the registers rather than directly on the memory. The instructions for data processing on registers are different from that access the memory.

- □ The instruction set of ARM is uniform and fixed in length. 32-bit ARM Processors have three instruction sets: general 32-bit ARM Instruction Set, 16- bit Thumb Instruction Set and Jazel]e instruction set.

- □ ARM supports **multiple stages of pipeline** to speed up the flow of instructions. In a simple three stage pipeline, the instructions follow: fetch, decode and execute.

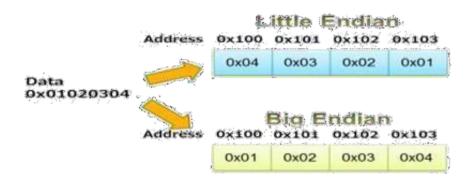

- Memory is byte addressable. Therefore, the word 0 in the ARM address space is at location 0, the word 1 is at location 4 and the word 2 is at the location 8 and so on, as a result the Program Counter (PC) is incremented by 4.

**Both little-endian and big-endian memory addressing.** The ARM processor can be configured at power-up to address the bytes in a word in either **little-endian mode** (with the lowest-order byte residing in the lowest storage address) or **Big-endian mode** (with the lowest-order byte residing in the highest storage address).

Figure 2.7 ARM Memory addressing

- ARM Processor used AMBA (Advanced Microcontroller Bus Architecture) bus interface.

AMBA is an open source specification for on- chip interconnect specifications from ARM that Standardizes on chip communication mechanisms between various functional blocks for building high performance System on Chip (SOC) designs.

- These designs typically have one or more micro controllers or microprocessors along with several other components-internal memory or external memory bridge, DSP, DMA, accelerators and various other peripherals like USB, UART, PCIE, I2C etc-all integrated on a single chip.

- The primary motivation of AMBA protocols is to have a standard and efficient way to interconnecting these blocks with re-use across multiple designs.

Figure 2.8 ARM Features

## Some of the general features of ARM are listed here.

- ARM Processors have a good speed of execution to power consumption ratio.

- They have a wide range of clock frequency ranging from 1MHz to few GHz.

- They support direct execution of Java bytecodes using ARM's Java Jazelle DBX.

- ARM Processors have built in hardware for debugging.

- Supports enhanced instructions for DSP operations.

# ARM ARCHITECTURE

ARM is a load-store reducing instruction set computer architecture; it means the core cannot directly operate with the memory. All data operations must be done by registers with the information which is located in the memory. Performing the operation of data and storing the value back to the memory. ARM consist of 37 register sets, 31 are general-purpose registers and 6 are status registers. The ARM uses seven processing modes that are used to run the user task.

# THE ARM ARCHITECTURE PROFILES

The ARM architecture profiles are:

# **1.** Application profile (ARMv7-A e.g. Cortex-A8)

Application profiles implement a traditional ARM architecture with multiple modes and support a virtual memory system architecture based on an MMU. These profiles support both ARM and Thumb instruction sets.

□ Features powerful processors found in high-end products like smartphones, tablets, or netbooks.

This includes the famous Cortex-A8 and Cortex-

A9 (in your super phone) processors.

# 2. Real-time profile (ARMv7-R e.g. Cortex-R4)

Real-time profiles im plement a traditional ARM architecture with multiple modes and support a protected memory system architecture based on an MPU.

$\hfill\square$  Can be found for example in control units for automotive systems or hard disk drive controllers.

They come with specific features suited to real-time environment constraints.

# 3. Microcontroller profile (ARMv7-M e.g. Cortex-M3)

Microcontroller profiles implement a programmers' model designed for fast interrupt processing, with hardware stacking of registers and support for writing interrupt handlers in high-level languages. The processor is designed for integration into an FPGA and is ideal for use in very low power applications. • They are smaller and used in numerous embedded systems like human interface devices, automotive control systems, power management systems, and others.

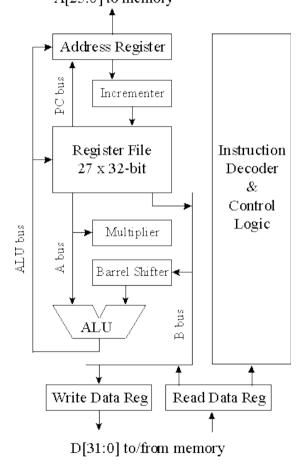

The ARM core is considered as a functional unit connected by data buses where,

- Arrow represents the flow of data

- Line represents the buses

- Boxes represents either an operation unit or storage area The functional units of the ARM architecture are, A[25:0] to memory

- □ Arithmetic and logic

unit  $\Box$  Booth multiplier

- □ Barrel shifter

- □ Control unit

- □ Register file

#### **Figure 2.9 ARM Architecture**

**Priority encoder:** The encoder is used in the multiple load and store instruction to point which register within the register file to be loaded or kept.

**Multiplexers:** Several multiplexers are accustomed to the management operation of the processor buses.

## Arithmetic Logic Unit(ALU)

The ALU has two 32-bits inputs. The primary comes from the register file, whereas the other comes from the shifter. Status registers flags modified by the ALU outputs. The V-bit output goes to the V flag as well as the Count goes to the C flag. Whereas the foremost significant bit

\_

really represents the S flag, the ALU output operation is done by NORed to get the Z flag. The ALU has a 4-bit function bus that perm its up to 16 opcode to be implemented.

## **Booth Algorithm**

Booth algorithm is a noteworthy multiplication algorithm ic rule for 2's complement numbers. This treats positive and negative numbers uniform ly. Moreover, the runs of 0's or 1's within the multiplier factor are skipped over without any addition or subtraction being performed, thereby creating possible quicker multiplication.

## **Barrel Shifter**

- □ The barrel shifter features a 32-bit input to be shifted. This input is coming back from the register file or it might be immediate data. The shifter has different control inputs coming back from the instruction register. The Shift field within the instruction controls the operation of the barrel shifter. This field indicates the kind of shift to be performed (logical left or right, arithmetic right or rotate right). The quantity by which the register ought to be shifted is contained in an immediate field within the instruction or it m ight be the lower 6 bits of a register within the register file.

- The shift\_val input bus is 6-bits, permitting up to 32bit shift. The shift type indicates the needed shift sort of 00, 01, 10, 11 are corresponding to shift left, shift right, an arithmetic shift right and rotate right, respectively. The barrel shifter is especially created with multiplexers.

#### **Control Unit**

For any microprocessor, control unit is the heart of the whole process and it is responsible for the system operation, so the control unit design is the most important part within the whole design. The control unit is sometimes a pure combinational circuit design. Here, the control unit is im plemented by easy state machine. The processor tim ing is additionally included within the control unit. Signals from the control unit are connected to each component within the processor to supervise its operation.

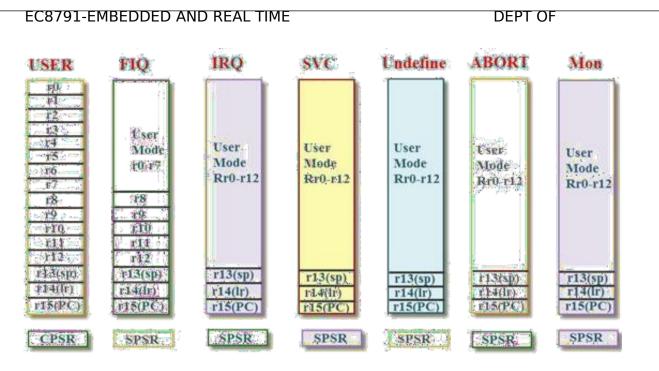

## ARM REGISTERS

The amount of registers depends on the ARM version. ARM has 37 registers all of which are 32-bits long. 1 dedicated Program Counter (PC), 1 dedicated Current Program Status Register (CPSR), 5 dedicated Saved Program Status Registers (SPSR) and 30 General Purpose

Registers.

The first 16 registers are accessible in user-level mode, the additional registers are available in priv ileged software execution. These 16 registers can be split into two groups: general purpose and special purpose registers.

**R0-R12:** can be used during common operations to store temporary values, pointers (locations to memory), etc. R0, for example, can be referred as accumulator during the arithmetic operations or for storing the result of a previously called function. R7 becomes useful while working with syscalls as it stores the syscall number and R11 helps us to keep track of boundaries on the stack serv ing as the frame pointer. Moreover, the function calling convention on ARM specifies that the first four arguments of a function are stored in the registers r0-r3.

| —E | EC8791-EMBEDDED AND REAL TIME DEP |              | PT OF |                                 |  |  |   |

|----|-----------------------------------|--------------|-------|---------------------------------|--|--|---|

|    |                                   | Regis<br>ter | Alias | Purpose                         |  |  | ] |

|    |                                   | R0           | _     | General purpose                 |  |  |   |

|    |                                   | R1           | _     | General purpose                 |  |  |   |

|    |                                   | R2           | _     | General purpose                 |  |  |   |

|    |                                   | R3           | _     | General purpose                 |  |  |   |

|    |                                   | R4           | _     | General purpose                 |  |  |   |

|    |                                   | R5           | _     | General purpose                 |  |  |   |

|    |                                   | R6           | _     | General purpose                 |  |  |   |

|    |                                   | R7           | _     | Holds Syscal Number             |  |  |   |

|    |                                   | R8           | _     | General purpose                 |  |  |   |

|    |                                   | R9           | _     | General purpose                 |  |  |   |

|    |                                   | R10          | _     | General purpose                 |  |  |   |

|    |                                   | R11          | FP    | Frame Pointer                   |  |  |   |

|    |                                   |              | Spe   | cial Purpose Registers          |  |  |   |

|    |                                   | R12          | IP    | Intra Procedural Call           |  |  |   |

|    |                                   | R13          | SP    | Stack Pointer                   |  |  |   |

|    |                                   | R14          | LR    | Link Register                   |  |  |   |

|    |                                   | R15          | РС    | Program Counter                 |  |  |   |

|    |                                   | CPSR         | _     | Current Program Status Register |  |  |   |

#### Table 2.2 ARM Registers

**R13: SP (Stack Pointer):** The Stack Pointer points to the top of the stack. The stack is an area of memory used for function-specific storage, which is reclaimed when the function returns.

**R14: LR (Link Register):** When a function call is made, the Link Register gets updated with a memory address referencing the next instruction where the function was initiated from. Doing this allows the program return to the "parent" function that initiated the "child" function call after the "child" function is finished.

**R15: PC** (**Program Counter**): The Program Counter is automatically incremented by the size of the instruction executed. This size is always 4 bytes in ARM state and

2 bytes in THUMB mode. When a branch instruction is being executed, the PC holds the destination address. During execution, PC stores the address of the current instruction plus 8 (two ARM instructions) in ARM state, and the current instruction plus 4 (two Thumb instructions) in Thumb(v1) state. This is different from x86 where PC always points to the next instruction to be executed.

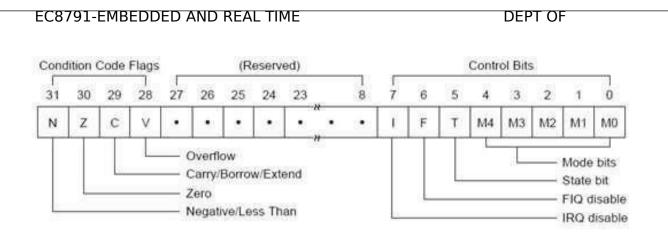

## Current Program Status Register (CPSR)

The Current Program Status Register (CPSR) holds:

- the APSR flags

- the current processor mode

- interrupt disable flags

- current processor state (ARM, Thumb, ThumbEE, orJazelje)

- endianness state (on ARMv4T andlater)

- execution state bits for the IT block (on ARMv6T2 and later).

# Figure 2.10 ARM CPSR

## **1.** Condition Bits N

- □ If this result is regarded as a two's complement signed integer,

- $\square$  then N = 1 If the result is negative and N = 0 if it is positive or

zero.

# Z

- Is set to 1 if the result of the instruction is zero and to 0 otherwise.

- □ This often indicates an equal result from a comparison.

# С

Is set in one of four ways:

- □ For an addition, including the comparison instruction CMN, C is set to 1 if the addition produced a carry and to 0 otherwise.

- For a subtraction, including the comparison instruction CMP, C is set to 0 if the subtraction produced a borrow (that is, an unsigned underflow), and to 1 otherwise.

- □ For non-addition/subtractions that incorporate a shift operation, C is set to the last bit shifted out of the value by the shifter.

- $\Box$  For other non-addition/subtractions, C is normal ly left unchanged

## V

Is set in one of two ways:

- For an addition or subtraction, V is set to 1 if signed overflow occurred, regarding the operands and result as two's complement signed integers.

- For non-addition/subtractions, V is normally left unchanged.

# **2.** Interrupt bit

I - Disables IRQ interrupts when it is set. F - Disables FIQ interrupts when it is set.

# **3.** Thumb Mode Bit

# T - Thumb mode

# 4. Mode Bits

5 bits that control what mode the CPU is in.

| M [4:0] | Mode       |

|---------|------------|

| 10000   | User       |

| 10001   | FIQ        |

| 10010   | IRQ        |

| 10011   | Supervisor |

| 10111   | Abort      |

| 11011   | Undefined  |

| 11111   | System     |

## Table 2.3 ARM Mode bits

## Saved Program Status Register (SPSR)

- The SPSR is used to store the current value of the CPSR when an exception is taken so that it can be restored after handling the exception. Each exception handling mode can access its own SPSR. User mode and System mode do not have an SPSR because they are not exception handling modes.

- The execution state bits, endianness state and current processor state can be accessed from the SPSR in any exception mode, using the MSR and MRS instruction.

## MODES OF OPERATION OF ARM PROCESSOR

The ARM uses seven processing modes that are used to run the user task.

- USER mode

- FIQ mode and IRQ mode

- SVC mode

- UNDEFINED mode

- ABORT mode

- THUMB mode

Figure 2.11 ARM Registers

- **1.** USER Mode: The user mode is a normal mode, which has the least number of registers. It doesn't have SPSR and has limited access to the CPSR.

- **2. FIQ and IRQ:** The FIQ and IRQ are the two interrupt caused modes of the CPU. The FIQ is processing interrupt and IRQ is standard interrupt. The FIQ mode has additional five banked registers to provide more flexibility and high performance when critical interrupts arehandled.

- **3. SVC Mode:** The Superv isor mode is the software interrupt mode of the processor to start up or reset.

- **4. Undefined Mode:** The Undefined mode traps when illegal instructions are executed. The ARM core consists of 32-bit data bus and faster data flow.

- **5. THUMB Mode:** In THUMB mode 32-bit data is div ided into 16-bits and increases the processing speed.

- **6. THUMB-2 Mode:** In THUMB-2 mode the instructions can be either 16-bit or 32-bit and it increases the performance of the ARM cortex –M3 microcontroller. The ARM cortex-m3 microcontroller uses only THUMB-2 instructions.

#### **ARM INSTRUCTIONSET**

• An Instruction Set Architecture (ISA) is part of the abstract model of a computer. It defines how software controls the CPU.

- DEPT OF The Arm ISA family allows developers to write software and firm ware that conforms to the Arm specifications, secure in the knowledge that any Arm- based processor will execute it in the same way. This is the foundation of the Arm portability and compatibility promise, underlying the Arm ecosystem.

- 2. Explain the operation of the BL instruction, including the state of ARM registers before and after its operation.

## ARM INSTRUCTION SET ARCHITECTURE

- > ARM processors have two main states they can operate in **ARM and Thumb**. The main difference between these two states is the instruction set, where instructions in ARM state are always 32-bit, and instructions in Thumb state are 16-bit (but can be 32-bit).

- > There are different Thumb versions. The different nam ing is just for the sake of differentiating them from each other (the processor itself will always refer to it as Thumb).

- Thumb-1 (16-bit instructions): was used in ARMv6 and earlier architectures. 0

- **Thumb-2** (16-bit and 32-bit instructions): extents Thumb-1 by adding more instructions 0 and allowing them to be either 16-bit or 32-bit wide (ARMv6T2, ARMv7).

- ThumbEE: includes some changes and additions aimed for dynamically generated code 0 (code compiled on the device either shortly before or during execution).

# ASSEMBLY LANGUAGE IN ARM

Assembly language is composed of instructions which are the main building blocks. ARM instructions are usually followed by one or two operands and generally use the following template:

# MNEMONIC{S}{condition} {Rd}, Operand1, Operand2

Due to flex ibility of the ARM instruction set, not all instructions use all of the fields prov ided in the template. Nevertheless, the purpose of fields in the template are described as follows:

- MNEMONIC Short name (mnemonic) of the instruction  $\geq$

- {S} An optional suffix. If S is specified, the condition flags are updated on the result of  $\geq$ the operation

- {condition}- Condition that is needed to be met in order for the instruction to be executed

- {Rd}- Register (destination) for storing the result of the  $\geq$ instruction. Operand1 - First operand, Either a register or an

immediate value

Operand2- Second (flex ible) operand. Can be an immediate value (number) or a register with an optional shift

While the MNEMONIC, S, Rd and Operand1 fields are straight forward, the condition and Operand2 fields require a bit more clarification. The condition field is closely tied to the CPSR register's value, or to be precise, values of specific bits within the register. Operand2 is called a flex ible operand, because we can use it in various forms – as immediate value (with lim ited set of values), register or register with a shift.

# **1.** DATA INSTRUCTION

The basic form of a data instruction is simple:

ADD r0,r1,r2

This instruction sets register r0 to the sum of the values stored in r1 and r2.

In addition to specify ing registers as sources for operands, instructions may also prov ide immediate operands, which encode a constant value directly in the instruction. For example,

ADD r0,r1,#2

sets r0 to r1 + 2.

# **2.** ARITHMETIC INSTRUCTION

The arithmetic operations perform addition and subtraction; the with-carry versions include the current value of the carry bit in the computation.

**RSB** performs a subtraction with the order of the two operands reversed, so

that RSB r0,r1,r2 sets r0 to be r2 - r1.

| ADD | Add                         |

|-----|-----------------------------|

| ADC | Add with carry              |

| SUB | Subtract                    |

| SBC | Subtract with carry         |

| RSB | Reverse subtract            |

| RSC | Reverse subtract with carry |

| MUL | Multiply                    |

| MLA | Multiply and accumulate     |

## Table 2.4 ARM arithmetic instruction

# **3.** LOGICAL INSTRUCTION

The bit-wise logical operations perform logical AND, OR, and XOR operations (the exclusive or is called EOR).

The **BIC** instruction stands for bit clear: BIC r0,r1,r2 sets r0 to r1 and not r2. This instruction uses the second source operand as a mask: Where a bit in the mask is 1, the corresponding bit in the first source operand is cleared. The MUL instruction multiplies two values, but with some restrictions: No operand may be an immediate, and the two source operands must be different registers.

The **MLA** instruction performs a multiply-accumulate operation, particularly useful in matrix operations and signal processing.

The instruction MLA r0,r1,r2,r3 sets r0 to the value r1 # r2 + r3.

| AND | Bit-wise and          |

|-----|-----------------------|

| ORR | Bit-wise or           |

| EOR | Bit-wise exclusive-or |

| BIC | Bit clear             |

# Table 2.5 ARM Logical instruction

4. SHIFT INSTRUCTIONS The shift operations are not separate instructions rather, shifts can be applied to arithmetic and logical instructions. The shift modifier is always applied to the second source operand.

A left shift moves bits up toward the most-significant bits, while a right shift moves bits down to the least-significant bit in the word.

The **LSL and LSR** modifiers perform left and right logical shifts, filling the leastsignificant bits of the operand with zeroes. The arithmetic shift left is equivalent to an LSL, but the ASR copies the sign bit, if the sign is 0, a 0 is copied, while if the sign is 1, a 1 is copied.

| LSL | Logical shift left (zero fil])  |

|-----|---------------------------------|

| LSR | Logical shift right (zero fil]) |

| ASL | Arithmetic shift left           |

| ASR | Arithmetic shift right          |

| ROR | Rotate right                    |

| RRX | Rotate right extended with C    |

## Table 2.6 ARM shift instructions

# **5.** ROTATE INSTRUCTIONS

The rotate modifiers always rotate right, moving the bits that falloff the least-

significant bit up to the most-significant bit in the word.

The **RRX** modifier performs a 33-bit rotate, with the CPSR's C bit being inserted above the sign bit of the word; this allows the carry bit to be included in the rotation.

# **6.** COMPARE INSTRUCTIONS

- Comparison operands do not modify general purpose registers but only set the values of the NZCV bits of the CPSR register.

- The compare instruction CMP r0, r1 computes r0 r1, sets the status bits, and throws away the result of the subtraction.

- CMN uses an addition to set the status bits.

- TST performs a bit-wise AND on the operands, while TEQ performs an exclusive-or.

## **Table 2.7 ARM Compare instructions**

| СМР | Compare         |

|-----|-----------------|

| CMN | Negated compare |

| TST | Bit-wise test         |

|-----|-----------------------|

| TEQ | Bit-wise negated test |

## **7.** MOVE INSTRUCTION

The instruction MOV r0,r1 sets the value of r0 to the current value of r1.

The MVN instruction complements the operand bits (one's complement) during the move.

| MOV | Move         |

|-----|--------------|

| MVN | Move negated |

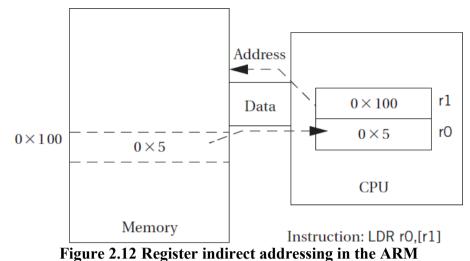

## Table 2.8 ARM Move instructions LOAD AND STOREINSTRUCTION

LDRB and STRB load and store bytes rather than whole words. LDRH and

SDRH operate on half-words.

LDRSH extends the sign bit on loading.

An ARM address may be 32 bits long. The ARM load and store instructions do not directly refer to main memory addresses, because a 32-bit address would not fit into an instruction that included an opcode and operands. Instead, the ARM uses register-indirect addressing. In register-indirect addressing, the value stored in the register is used as the address to be fetched from memory; the result of that fetch is the desired operand value.

| LDR   | Load                    |

|-------|-------------------------|

| STR   | Store                   |

| LDRH  | Load half-word          |

| STRH  | Store half-word         |

| LDRSH | Load half-word signed   |

| LDRB  | Load byte               |

| STRB  | Store byte              |

| ADR   | Set register to address |

Table 2.9. ARM Load and Store instructions

DEPT OF

# 8. CONDITIONAL INSTRUCTION

The B (branch) instruction is the basic mechanism in ARM for changing the flow of control.

| EQ | Equals zero Z=1                      |

|----|--------------------------------------|

| NE | Not equal to zero Z=0                |

| CS | Carry set C=1                        |

| CC | Carry clear C=0                      |

| MI | Minus N=1                            |

| PL | Nonnegative (plus) N=0               |

| VS | Overflow V=1                         |

| VC | No overflow V=0                      |

| HI | Unsigned higher C=1 and Z=0          |

| LS | Unsigned lower or same C=0 or Z=1    |

| GE | Signed greater than or equal N=V     |

| LT | Signed less than N=V                 |

| GT | Signed greater than Z=0 and N=V      |

| LE | Signed less than or equal Z=1 or N=V |

#### **Table 2.10 ARM Conditional instructions**

Instructions are branched conditionally, based on the result of a given computation. The if statement is a common example. The ARM allows any instruction, including branches, to be executed conditionally. This allows branches to be conditional, as wellas data operations.

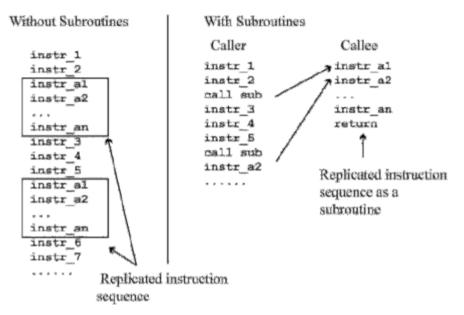

## STACKS AND SUBROUTINES

# **1.** SUBROUTINES

Large programs are hard to handle and so broken into smaller programs called as subroutines. A subroutine is a block of code that is called from different places from within a main program or other subroutines.

Figure 2.13 ARM subroutine.

A subroutine can have

- parameters that control its operation

- local variables for computation

Only the code for the subroutine callis repeated.

A subroutine may pass a return value back to the caller.

# WRITING SUBROUTINES

When using subroutines, it is necessary to know the following:

- When should we jump? (use CALL)- A subroutine call can be implemented by pushing the return address on the stack and then jumping to the branch target address.

- Where do we return to? (use RETURN)- When the subroutine is done, remember to pop out the saved information so that it will be able to return to the next instruction immediately after the calling point.

Subroutines are based on MPU instructions and use STACK

A **Branch and Link** (BL) instruction is used to call a subroutine or a procedure in ARM. For instance,BL foo /\*BL- Branch and link instruction, foo is a subroutine/procedure name\*/ will perform a branch and link to the code starting at location.

The branch and link is much like a branch, except that before branching it stores the current PC value in r14. Thus, to return from a procedure, simply move the value of r14 (LR) to r15(PC)

## MOV r15,r14

When subroutines are nested, the contents of the link register must be saved on a stack by the subroutine. Register R13, Stack Pointer is normally used as the pointer for this stack But this mechanism only lets us callprocedures one level deep.

If, for example, we call a C function within another C function, the second function call will overwrite r14, destroying the return address for the first function call. The standard procedure for allowing nested procedure calls (including recursive procedure calls) is to build a stack, as illustrated in Figure 2.14. The C code shows a series of functions that call other functions: f1() calls f2(), which in turn calls f3(). The right side of the figure shows the state of the procedure call stack during the execution of f3(). The stack contains one activation record for each active procedure. When f3() finishes, it can pop the top of the stack to get its return address, leaving the return address for f2() waiting at the top of the stack for its return.

```

void f1(int a) [

f2(a);

}

f3

void f2(int r) [

f3(r,5);

f2

Growth

}

void f3(int x, int y) {

f1

g = x + y;

}

Function call stack

main() [

f1(xyz);

C code

```

We can also use the procedure call stack to pass parameters. The conventions used to pass values into and out of procedures are known as **procedure linkage**.

To pass parameters into a procedure, the values can be pushed onto the stack just before the procedure call. Once the procedure returns, those values must be popped off the stack by the caller, because they may hide a return address or other useful information on the stack.

A procedure may also need to save register values for registers it modifies. The registers can be pushed onto the stack upon entry to the procedure and popped off the stack, restoring the previous values, before returning.

- Procedure stacks are typically built to grow down from high addresses.

- Assembly language programmers can use any means they want to pass parameters. Compilers use standard mechanisms to ensure that any function may callany other. The compiler passes parameters and return variables in a block of memory known as a **frame**. The frame is also used to allocate local variables. The stack elements are frames.

- A stack pointer (sp) defines the end of the current frame, while a frame pointer (fp) defines the end of the last frame. (The fp is technically necessary only if the stack frame can be grown by the procedure during execution).

- $\circ$  The procedure can refer to an element in the frame by addressing relative to sp.

- When a new procedure is called, the sp and fp are modified to push another frame onto the stack.

- The ARM Procedure Call Standard (APCS) is a good illustration of a typical procedure linkage mechanism. Although the stack frames are in main memory, understanding how registers are used is key to understanding the mechanism, as explained below.

- r0-r3 are used to pass the first four parameters into the procedure. r0 is also used to hold the return value. If more than four parameters are required, they are put on the stack frame.

- ➢ r4-r7 hold register variables.

- $\succ$  r11 is the frame pointer and r13 is the stack pointer.

- > r10 holds the limiting address on stack size, which is used to check for stack overflows.

Other registers have additional uses in the protocol.

Example: Procedure Calls in ARM Here is a simple example of two procedures, one of which calls another: void f2(int x) { int y; y = x+1; } void f1(int a) { f2(a); }

This function has only one parameter, so x will be passed in r0. The variable y is local to the procedure so it is put into the stack. The first part of the procedure sets up registers to manipulate the stack, then the procedure body is implemented.

## 2.4.2 STACK

Stack is a Temporary memory storage space by MPU during the execution of a program.

The stack is a data structure, known as last in first out (LIFO). In a stack, items entered at one end and leave in the reversedorder.

Stacks in m icroprocessors are implemented by using register called the stack pointer, sim ilar to the program counter (PC), to keep track of available stack locations. As items are added to the stack (pushed), the stack pointer is moving up, and as items are removed from the stack (pulled or popped),

the stack pointer is moved down.

## Instructions to Store and Retrieve Information from the Stack

**PUSH:** Increment the memory address in the stack pointer (by one) and stores the contents of the Program counter on the top of the stack

POP: Discards the address of the top of the stack and decrement the stack pointer by one

# STACK TYPES

ARM stacks are very flexible since the implementation is completely left to the software. Stack pointer is a register that points to the top of the stack. Normally, there are four different stack implementations depending on which way the stack grows.

## **1.** Ascending stack

An Ascending stack grows upwards. It starts from a low memory address

and, as items are pushed onto it, progresses to higher memory addresses.

#### **2.** Descending stack

A Descending stack grows downwards. It starts from a high memory address, and as items are pushed

onto it, progresses to lower memory addresses. The previous examples have been of a Descending stack.

#### **3.** Empty stack

In an Empty stack, the stack pointers points to the next free (empty) location on the stack, i.e. the place where the next item to be pushed onto the stack will be stored.

## 4. Full stack

In a Full stack, the stack pointer points to the topmost item in the stack, i.e. the location of the last item to be pushed onto the stack.

## 4. Explain the peripherals for LPC214X family in ARM processor.

## LPC2148 PROCESSOR

It is an ARM7 based processor with ARM7TDMI-S Processor core. It is based on ARMv4 architecture and the significant changes from its previous architecture is the introduction of the 16-bit Thumb instructions.

LPC2148 is manufactured by NXP Semiconductor (Phillips) and it is preloaded with many inbuilt features and peripherals. This makes it more efficient and reliable choice for an high-end application developer.

The ARM7 is a 32-bit general-purpose microprocessor, and it offers some of the features like little power utilization, and high performance. The architecture of an ARM is depended on the principles of RISC. The associated decode mechanism, as well as the RISC- instructions set are much easy when we compare with microprogrammed CISC-Complex Instruction Set Computers.

The Pipeline method is used for processing all the blocks in architecture. In general, a single

#### DEPT OF

instruction set is being performed, then its descendant is being translated, & a 3rd-instruction is being obtained from the memory.

An exclusive architectural plan of ARM7 is called as Thumb, and it is perfectly suitable for high volume applications where the compactness of code is a matter The ARM7 also uses an exclusive architecture namely Thumb. It makes it perfectly suitable for different applications by memory limitations where the density of code is a matter.

## **FEATURES OF LPC2148**

The main features of LPC2148 include the following.

- The LPC2148 is a 16 bit or 32 bit ARM7 family based microcontrolJer available in a smallLQFP64 package.

- ISP (in system programming) or IAP (in application programming) using on-chip boot loader software.

- On-chip static RAM is 8 kB-40 kB, on-chip flash memory is 32 kB-512 kB, the wide interface is 128 bit, or accelerator allows 60 MHz high-speed operation.

- It takes 400 milji seconds time for erasing the data in fuljchip and 1 miljisecond time for 256 bytes of programming.

- Embedded Trace interfaces and Embedded ICE RT offers real-time debugging with high-speed tracing of instruction execution and on-chip Real Monitor software.

- It has 2 kB of endpoint RAM and USB 2.0 fullspeed device controller.

Furthermore, this microcontroller offers 8kB on-chip RAM nearby to USB with DMA.

- One or two 10-bit ADCs offer 6 or 14 analog i/ps with low conversion time as 2.44 µs/ channel.

- Only 10 bit DAC offers changeable analog o/p.

- External event counter/32 bit timers-2, PWM unit, & watchdog.

- Low power RTC (real time clock) & 32 kHz clockinput.

## DEPT OF

- Several serial interfaces like two 16C550 UARTs, two I2C-buses with 400 kbit/s speed.

- 5 volts tolerant quick general purpose Input/output pins in a small LQFP64 package.

- Outside interrupt pins-21.

- 60 MHz of utmost CPU CLK-clock obtainable from the programmable-on-chip phase locked loop by resolving time is 100 μs.

- The incorporated oscillator on the chip will work by an exterior crystal that ranges from 1 MHz-25 MHz

- The modes for power-conserving mainly comprise idle & powerdown.

- For extra power optimization, there are individual enable or disable of peripheral functions and peripheral CLK scaling.

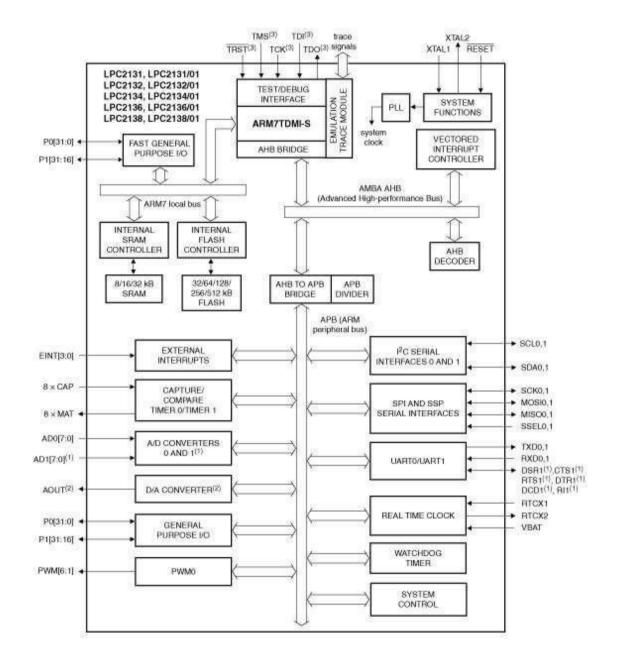

## 5. EXPLAIN THE ARCHITECTURE BLOCK DIAGRAM OF LPC2148

LPC 2148 m icrocontroller consist of three buses such as ARM7 Local bus, AHB (Advanced high performance bus) and VPB bus etc. these buses are used for performing different function and these are also consisting of different functioning parts such as,

- Using serial built in JTAGInterface

- Using In-System Programming (ISP)

- By means of In-Application Programming (IAP) capabilities

The application program, using IAP functions may also erase and/or program the FLASH while the application is running. When the LPC2148 on chip bootloader is used, 500kB of flash memory is available for user code.

**Static RAM Memory System**: LPC2148 prov ides 32kB of static RAM which may be used for code and/or data storage. It may be accessed as 8-bit, 16-bit and 32-bits.

# EC8791-EMBEDDED AND REAL TIME Interrupt sources

Every peripheral dev ice consists of a single interrupt line allied to the VIC (vector interrupt controller. All input requests are received by vectored interrupt controller (VIC) and it converts them into fast interrupt request (FIQ). So, fast interrupt request and non-fast interrupt requests are defined by programm ing setting in vectored interrupt controller.

# EC8791-EMBEDDED AND REAL TIME **Pin Connect Block**

This block perm its chosen pins of the ARM7 based LPC2148 m icrocontroller for having several functions. The multiplexers can be controlled by the configuration registers for allowing the link between the pin as well as on-chip peripherals. Peripherals must be coupled with the suitable pins prev ious to being triggered, and prev ious to any connected interrupts being perm itted. The microcontroller functionality can be defined by the pin control module by its pin selection of registers in a given hardware env ironment. After rearranging all pins of ports (port 0 & port 1) are arranged as i/p by the given exceptions. If debug is allowed, the pins of the JTAG will guess the functionality of JTAG. If a trace is allowed, then the Trace pins will guess the functionality of trace. The pins connected to the I2C0 and I2C1 pins are open drain.

## PERIPHERALS

## **GPIO (General Purpose Input Output)**

ARM based LPC2148 m icrocontroller has 45 general purpose input output pins. The operating voltage of these input output pins is 5 volts.

GPIO registers control the dev ice pins which are not linked to a particular periphera l function. The device pins can be arranged as i/p or o/p. Indiv idual registers allow for clearing any number of o/p's concurrently. The output register value can be read back, & the present condition of the port pins.

LPC2148 has two IO ports each of 32-bit wide, prov ided by 64 IO pins. Ports are named as P0 and P1. Pins of each port labelled as Px.y where "x" stands for port number, 0 or 1. Where "y" stands for pin number usually between 0 to 31. Each pin can perform multiple functions. For example: Pin no.1 which is P0.21 serves as GPIO as well as PWM5, AD1.6 (A/D converter1, input 6), CAP1.3 (Capture input for Timer1, Channel 3).

#### Digital to analog Converter:

This LPC2148 m icrocontroller has one 10 bit digital to analog converter (DAC). This converter converts the digital input into analog output. The maximum DAC output voltages are called VREF voltages. Power down mode and buffered output is also available in this digital to analog converter.

#### **10-bit ADC (Analog to Digital Converter)**

EC8791-EMBEDDED AND REAL TIME DEPT OF The microcontrollers like LPC2144/46/48 include two ADC converters ADC0 and ADC1, and are only 10-bit straight approx imation ADC's. Although ADC0 includes 6- channels and ADC1 has 8- channels.

## 10-bit DAC (Digital to Analog Converter)

This LPC2148 m icrocontroller has one 10 bit digital to analog converter (DAC). This converter converts the digital input into analog output. The maximum DAC output voltages are called VREF voltages. Power down mode and buffered output is also available in this digital to analog converter.

#### **Device Controller-USB 2.0**

The universal serial bus consists of 4-wires, and that gives the support for communication between a number of peripherals and hosts. This controller allows the bandwidth of USB for connecting devices using a protocol based on thetoken.

The bus supports unplugging hot plugging and dynamic collection of the devices. Every communication is started through the host-controller. These microcontrollers are designed with a universal serial bus apparatus controller that allows 12 Mbit/sec data replaced by a host controller of USB.

#### UARTs

LPC2148 include two UARTs whose name are UART 0 and UART 01 for standard transmit & get data- lines. This LPC2148 m icrocontroller contains two UART whose name are UART 0 and UART 01. These UARTs are provided the full mode control handshake interface during transm itting or receiv ing the data lines. These are used 16 Byte data rate during transmitting or receiv ing the data. For covering wide range of baud rate, they also contain the built-in functional baud rate generator, therefore there is no need of any external crystal of specific value.

#### Serial I/O Controller of I2C-bus

LPC2148 includes two I2C bus controllers, and this is bidirectional. The inter-IC control can be done with the help of two wires namely an SCL and SDA. Here the SDA & SCL are serial clock line and the serial data line.

Every apparatus is identified by an indiv idual address. Here, transmitters and receivers can work in two modes like master mode/slave mode. This is a multi- master bus, and it can be managed by one or more bus masters linked to it. These microcontrollers support up to-400

# EC8791-EMBEDDED AND REAL TIME kbit/s bit rates.

#### SPI Serial Input/Output Controller

These microcontrollers include a single SPI controller and intended to handle numerous masters & slaves associated with a specified bus.

Simply a master & a slave can converse over the interface throughout specified data transmission. During this, the master constantly transmits a byte-of-data toward the slave, as weljas the slave constantly transmits data toward the master.

#### SSP Serial Input/Output Controller

These microcontrollers contain single SSP, and this controller is capable of process on an SPI, Microwire bus or 4-wire SSI. It can communicate with the bus of several masters as wellas slaves

But, simply a particular master, as well as slave, can converse on the bus throughout a specified data transm it. This m icrocontroller supports full-duplex transfers, by 4-16 bits data frames used for the flow of data from the master- the slave as well as from the slave-the master.

#### **Timers/Counters**

Timers and counters are designed for counting the PCLK (peripheral clock) cycles & optionally produce interrupts based on 4-match registers.

This LPC2148 microcontroller has two timers or counters. These timers are 32 bit and are programmable with 32bit pre scaler value as well as it also has one externa 1 event counter. Each timer has four 32bit capture channels which take the snapshot of timer value during the transition of any input signal. W ith the help of this capture event the interruption could be also generate.

#### Watchdog Timer

LPC2148 microcontroller contains watchdog timer is used for resetting the microcontroller in a reasonable sum of time. When it is allowed then the timer will produce a reset of a system if the consumer program does not succeed to reload the timer in a fixed sum of time.

#### **RTC-Real-time Clock**

The RTC in LPC2148 is intended for providing counters to calculate the time when the idle

EC8791-EMBEDDED AND REAL TIME DEPT OF or normal operating method is chosen. The RTC uses a small amount of power and designed for appropriate battery power-driven arrangements where the central processing unit is not functioning constantly.

#### **Power Control**

These microcontrollers support two condensed power modes such as power-down mode and idle mode. In Idle mode, instructions execution is balanced until an interrupt or RST occurs. The functions of peripheral maintain operation throughout idle mode & can produce interrupts to cause the CPU to restart finishing. Idle mode removes the power utilized by the CPU, controllers, memory systems, and inner buses.

In power down mode, the oscillator is deactivated and the IC gets no inner clocks. The peripheral registers, processor condition with registers, inner SRAM values are conserved during Power-down mode & the chip logic levels output pins stayfixed.

This mode can be finished and the common process restarted by specific interrupts that are capable to work without clocks. Because the chip operation is balanced, Power-down mode decreases chip power utilization to almost zero.

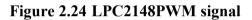

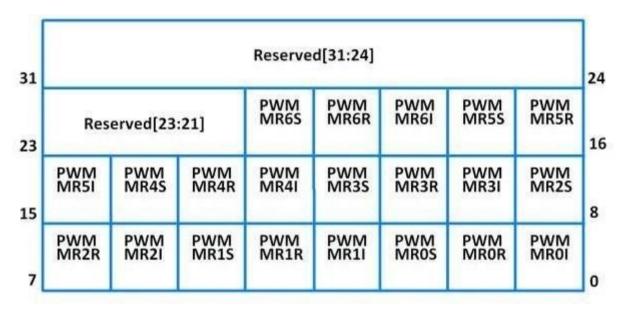

#### 5. Explain the concept of PWM -Pulse Width Modulator

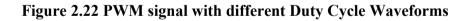

The PWMs are based on the normal timer-block & also come into all the features, though simply the pulse width modulator function is fixed out on the microcontrollers like LPC2141/42/44/46/48.

The timer is intended to calculate PCLK (peripheral clock) cycles & optionally produce interrupts when particular timer values arise based on 7-match registers, and PWM function also depends on match register events.

The capability of indiv idually control increasing & decreasing boundary positions allows the pulse width modulation to be utilized for several applications. For example, the typical motor control with multi-phase uses 3-non-overlapping outputs of PWM by separate control of every pulse widths as wellas positions.

#### **VPB** Bus

#### DEPT OF

The VPB div ider resolves the association between the CCLK (processor clock) and the PCLK (clock used by peripheral dev ices). This div ider is used for two purposes. The first use is to supply peripherals by the preferred PCLK using VPB bus so that they can work at the selected speed of the ARM processor. In order to accomplish this, this bus speed can be reduced the clock rate of the processor from 1/2 - 1/4.

Because this bus must work accurately at power-up, and the default state at RST (reset) is for the bus to work at 1/4th of the processor clock rate. The second use of this is to perm it power savings whenever an application doesn't need any peripherals to work at the complete processor rate. Since the VPB-div ider is associated with the output of PLL, this remains active throughout an idle mode.

#### **Emulation & Debugging**

The microcontroller (LPC2141/42/44/46/48) holds emulation & debugging through serial port-JTAG. A trace-port perm it tracing the execution of the program. Trace functions & debugging concepts are multiplexed with port1 and GPIOs.

Code Security The code security feature of these microcontrollers 2141/42/44/46/48 perm its a function to control whether it can be protected or debugged in inspection.

| LPC 2148 PIN DESCRIPT ( Chi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|

| LPC 2148 PIN DESCRIPTEON CITED AND C | Vbat                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                       |

| LPC2148 m icrocontroller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | a date se pins is called a port. It                   |

| P0.21/PWM5/AD1.6/CAP1.3 10<br>compaists and 78000 ponts could be                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 48 P1.20/TraceSync                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | E                                                     |

| therefore the prins of these ports are called GPIO (general purpo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 46 P0.16/EintO/MAT0.2/CAP0.2<br>OSes put-output pins. |

| RTCX2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 44 P1.21/PipeStat0                                    |

| Vss 6 Figure 2.17 LPC2148 Pin diag                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ram <sup>3</sup> ∎Vdd                                 |